Finite State Machine Serial Adder

Abstract— Logic design is in itself bifurcated to- Combinational and Sequential circuits. The later has memory and former doesn’t, so in an advent effort to incorporate memory into a combinational circuit brought in the concept of Finite state machine serial adder.

Keywords— D-latch, Finite state machine, Mealy Model, Multisim, Serial adder

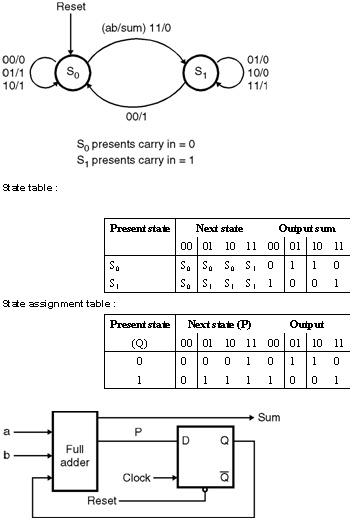

State diagram for serial adder: Let S0 and S1 are the states where the carry in values is '0' and '1' respectively. Figure shows the suitable state diagram defined as a mealy model. The output value sum depends on both state and the present value of the inputs a and b, each transition is labeled using the notation ab / sum which indicates the. Using the FSM VHDL code template provided above, you will implement a Finite State Machine in its canonical implementation. Moreover, you should be able to implement you own Vending Machine in VHDL! If you appreciated this post, please help us to share it with your friend.

I. INTRODUCTION TO FINITE STATE MACHINE

A finite state machine can be represented by a state transition table or a state diagram. There is often a fixedstart state which is the initial state of the Finite State Machine (before any input has been read). Thus a finite state machine (FSM) is a model describing the behavior of a finite number of states, the transitions between those states, and actions [1].

II. SERIAL ADDER

The serial binary adder or bit-serial adder is a digital circuit that performs binary addition bit by bit. The serial full

adder has three single-bit inputs, two for addition and one for carry in(C-in). There are two single-bit outputs for the sum and carry out(C-out). The C-in signal is the previously calculated C-out signal. Adding each bit, lowest to highest, one per clock cycle, performs the addition [2]. Fig 1 shows a basic structure of a FSM serial adder.

Fig 1: Block diagram of a serial adder[2]

The design is based on Mealy model. Let us consider two states, G & H i.e. when carry is generated we take H state &

when carry is zero we take G state. A & B are taken as the inputs to the serial adder. Table 1 shows the state table of the serial adder [2].

Table 1: STATE TABLE of SERIAL ADDER[2]

Based on the state table we can construct the state diagram. The state diagram is as shown in Fig 2. As observed in the state figure as long as the there is no carry generated, it stays in state G. but if there is a carry generated, it immediately moves to state H. In this state carry is added to the sum. When sum of A & B does not create a carry it moves back to state G.

VHSIC [Very High Speed Integrated Circuits] Hardware Description Language

IEEE-1076

This is just a quick reference of some short VHDL code fragments. Above each code segment is a circuit which represents the fragment.

In most cases the Process, and end of Process commands are not listed to keep the text down.

VHDL code for a D Flip Flop

process (signal names)

begin

if (clock’event and clock = ‘1’) then

output <= data;

end if;

end process

A 1 bit flip flop is used as the example. but any data width may be used.

Reference; a D Flip Flop Definition and true table.

VHDL code for a D Flip Flop with Reset and Clear Hp laserjet m1132 mfp driver for mac download.

if reset = ‘0’ then

output <= ‘0’;

elsif set = ‘0’ then

output <= ‘1’;

elsif (clock’event and clock = ‘1’) then

output <= data;

end if;

Note that the code show asynchronous Reset and Clear lines, which is fine for the code segment.

However those lines should be synchronized at some point, or insure that no data is used when those lines are valid.

VHDL code for a D Flip Flop

if (clock’event and clock = ‘0’) then

if (reset = ‘0’ and data = ‘0’) then

output <= ‘0’;

elsif (reset = ‘0’ and data = ‘1’) then

output <= ‘0’;

elsif (reset = ‘1’ and data = ‘0’) then

output <= ‘0’;

elsif (reset = ‘1’ and data = ‘1’) then

output <= ‘1’;

end if;

Another flip flop using a reset, but this time just to zero out the data, as in a gating signal.

Again, the rest signal should have been synchronized with the clock at some point [in another code fragment].

VHDL code for a JK Flip Flop

if (clock’event and clock = ‘1’) then

if (in1 = ‘0’ and in2 = ‘0’) then

output <= output;

elsif (in1 = ‘1’ and in2 = ‘0’) then

output <= ‘1’;

elsif (in1 = ‘0’ and in2 = ‘1’) then

output <= ‘0’;

elsif (in1 = ‘1’ and in2 = ‘1’) then

output <= not(output);

end if;

end if;

Reference; a JK Flip Flop Definition and true table.

VHDL code for a 2-to-1 Mux

Vhdl Code For Serial Adder Using Finite State Machine Diagram

if sel = ‘0’ then

output <= data1;

elsif sel = ‘1’ then

output <= data2;

end if;

Reference Standard Logic Multiplexer Circuits.

This circuit may be scaled to any data width, and more complicated select functions can be implemented.

VHDL code for a Serial to Parallel Converter

if clear = ‘0’ then

shift_reg <= “00000000”;

elsif (clock’event and clock = ‘1’) then

shift_reg(7 downto 1) <= (6 downto 0);

shift_reg(0) <= serial;

end if;

A common 8 bit data path is coded as an example.

Reference Common Shift Register Functions.

VHDL code for a Parallel to Serial Converter

if load = ‘0’ then

shift_reg <= parallel;

elsif (clock’event and clock = ‘1’) then

serial <= shift_reg(7);

shift_reg(7 downto 1) <= (6 downto 0);

end if;

A common 8 bit data path is coded as an example.

Reference Common Shift Register Functions.

VHDL code for a 4 bit Counter

if load = ‘0’ then

output <= “1111”;

elsif (clock’event and clock = ‘1’) then

output <= data - ‘1’;

end if;

carry <= ‘0’ when output = “0000” else‘1’;

load <= carry;

The code provides a 4 bit down counter function.

Reference common logic functions; Up/Down Decade Counters, or Up/Down Binary Counters.

VHDL code for a 1 bit Adder

if c = ‘0’ then

if (a and b) = ‘1’ then

sum <= ‘0’;

carry <= ‘1’;

elsif (a or b) = ‘1’ then

sum <= ‘1’;

carry <= ‘0’

end if;

elsif c = ‘1’ then

if (a and b) = ‘1’ then

sum <= ‘1’;

carry <= ‘1’;

elsif (a or b) = ‘1’ then

sum <= ‘0’;

carry <= ‘1’;

end if;

end if;

An adder could be a half adder which does not accept a carry in or a full adders that uses a carry input [as shown].

It's assumed that these inputs are some how synchronized with a clock.

Reference; Types of IC Adders, with logic diagram.

VHDL code for a State Machine

Vhdl Code For Serial Adder Using Finite State Machine Calculator

if reset = ‘0’ then

state <= stateA;

output <= ‘0’;

elsif (clock’event and clock) = ‘1’ then

case state is

when stateA

output <= ‘0’;

state <= stateB

when stateB

output <= ‘1’;

if input = ‘1’ then

state <= stateB;

else

state <=stateC;

end if;

when stateC

output <= ‘0’

state <= stateA;

end case;

Exclusive-OR Gate

if (a and b) = ‘1’ then

y <= ‘0’;

elsif (a and b) = ‘0’ then

y <= ‘0’;

else

y <= ‘1’;

end if;

Reference; a Exclusive-OR Gate Definition and true table.

IEEE-1076: Standard VHDL Language Reference Manual IEEE Computer Society Document

IEEE 1076.1: VHDL Analog and Mixed-Signal Extensions IEEE Computer Society Document

IEEE 1076.2: Standard VHDL Mathematical Packages IEEE Computer Society Document

IEEE 1076.3: Standard VHDL Synthesis Packages IEEE Computer Society Document

IEEE 1076.4: Standard for VITAL ASIC (Application Specific Integrated Circuit) Modeling Specification IEEE Computer Society Document

IEEE 1076.6: Standard for VHDL Register Transfer Level (RTL) Synthesis IEEE Computer Society Document

Links on this site:

VHDL Sites: Listed here

Back to the Logic Design Page, Digital Logic Pitfalls

VHDL Design Tools: CAD - CAE Products

VHDL Simulation Tools: VHDL Simulation Software Products

FPGA Manufactures: Hardware - Components - Semiconductor- Digital - Programmable Logic

Wineskin mac instalar. In regards to flip-flops and other examples, there are no constraints on using standard functions.

That is a flip flop does not have to be constrained to a D-type or JK-type function, any number of commands might be used.

The functions provided do relate to an available IC function so comparisons can be made between the firmware and hardware.

| Home | |||||||

| Distributors | Components | Equipment | Software | Standards | Buses | Design | Reference |

© 1998 - 2016 All rights reserved Larry Davis